# LABORATORY MANUAL FOR

# Lab Course EL 491

## **Electronics Circuit Design Laboratory**

#### **CONTENTS**

- 1. Quadrature Oscillator

- 2. Switch Capacitor

- 3. OTA Multi-function Filters

- 4. Precision Rectifiers using Bi-phase Amplifiers

- 5. CFA (Current Conveyer)

- 6. Opamp-based Multi-function Filters

- 7. Appendix I (Precautions)

- 8. Appendix –II (Data on the ICs CD4066 & CA3080)

# Muhammad Hadi Ali Khan

Electronics Engineer,

Department of Electronics Engineering,

A. M. U., Aligarh - 202 002, India

Phone & Fax: +91-571-2721148 (Office)

Email: - hadialikhan@gmail.com

**NB**:- This laboratory manual is also available on the Internet and can be downloaded from:-

http://hadialikhan.tripod.com/lab491.pdf

#### **Electronic Circuits Design Laboratory**

#### Lab. Course EL – 491

#### Experiment No. 01 (Quadrature Oscillator)

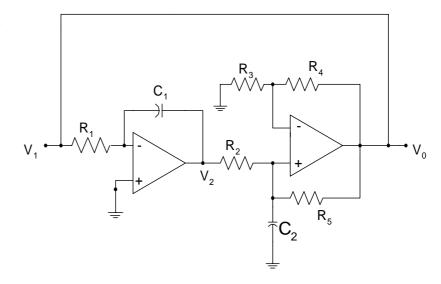

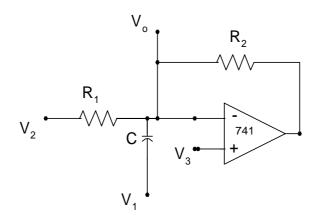

Circuit Diagram:-

Theory:- On analyzing the circuit of the quadrature oscillator, shown above, the condition

of the oscillation may be written as:  $\frac{R_4}{R_3} = \frac{R_5}{R_2}$  ----- (1)

And the frequency of oscillation can be expressed as  $\omega^2 = \frac{1 + \frac{R_4}{R_3}}{R_1 R_2 C_1 C_2}$ ,

or,

$$f = \frac{1}{2\pi} \sqrt{\frac{1 + \frac{R_4}{R_3}}{R_1 R_2 C_1 C_2}}$$

,

Taking

$$R_3 = R_4$$

and  $C_1 = C_2 = C$ ,  $f = \frac{1}{2\pi C} \sqrt{\frac{2}{R_1 R_2}}$  ---- (2)

#### Design:-

For design frequency (given), assume appropriate values of R1 & C, and calculate  $R_2 = \dots K\Omega$ ,

Corresponding to the nearest available value of the resistor, calculate f by back calculations.

#### **Observations:-**

Use a pot of 10 K $\Omega$  for  $(R_3 + R_4)$  and adjust it to get the output waveform Vo. Once the output Vo is obtained corresponding to the particular values of  $R_1$  and  $R_2$ , replace  $R_1$  by a few discrete values of resistors such as 2.2 K $\Omega$ , 3.3 K $\Omega$ , 4.7 K $\Omega$  etc., and measure the frequency of  $V_o$  corresponding to each of these values and verify that the frequency is changing but the phase difference between  $V_o$  and  $V_2$  is always  $90^o$ .

| $R_1$ (K $\Omega$ ) | Time period (µs) | Practical value of frequency (KHz) | Theoretical value of frequency (KHz) |

|---------------------|------------------|------------------------------------|--------------------------------------|

|                     |                  |                                    |                                      |

|                     |                  |                                    |                                      |

|                     |                  |                                    |                                      |

|                     |                  |                                    |                                      |

#### **Sample Calculations**:

Designed frequency = ------ KHz Measured frequency = ----- KHz %age error = ----- % Plot a curve between  $R_1$  & f.

\*\*\*\*\*\*

#### **Electronic Circuits Design Laboratory**

#### Lab. Course EL – 491

#### Experiment No. 02 (Switch Capacitor)

Theory:-

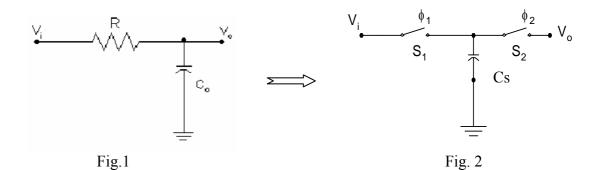

The resistor R, in figure 1 can be simulated by a capacitor  $C_s$ , connected between two switches  $S_1$  and  $S_2$ , turning ON and OFF by the two non-overlapping pulses  $\phi_1$  and  $\phi_2$  at the switching frequency  $f_C$ , as shown in figure 2.

The transfer function of the above low-pass section is given by the expression:

$$\frac{\text{Vo}}{\text{Vi}} = \frac{(1/RC_o)}{s + (1/RC_o)}, \text{ which gives } \omega_o = \frac{1}{RC_o},$$

Therefore,

$$f_0 = \frac{1}{2\pi RC_a}$$

.... (1)

With reference to figure 1 & 2, the current through R is  $\epsilon = C_s \frac{dv}{dt} = C_s \frac{V_1 - V_2}{T_C} = \frac{V_1 - V_2}{R}$

Therefore,

$$R = \frac{T_C}{C_s} = \frac{1}{C_s f_C}$$

, .... (2),

Substituting the value of R obtained from equation (1) into equation (2) yields

$$f_o = \frac{C_S f_C}{2\pi C_o} \, .$$

or,

$$\frac{f_C}{f_O} = 2\pi \left(\frac{C_O}{C_S}\right)$$

Take

$$\frac{f_c}{f_o} = (2 \text{ to } 30)$$

,

<u>Design</u>: For your design frequency  $f_o =$  ------ Hz , (given), Choose  $C_o =$  ------  $\mu F$ , Now using  $f_c = 30 f_o$ , Calculate  $C_S =$  ... , Take  $C_S =$  ------  $\mu F$ , & calculate  $f_C =$  ----

The practically used values are

$$C_0 = ---- \mu F$$

$C_S = ---- \mu F$

$f_0 = ---- KHz$

$f_C = ---- KHz$

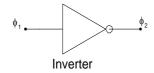

Note: Use a NAND gate (TTL IC 7400) as an inverter (NOT gate), to get non-overlapping pulses and a CMOS IC, CD 4066 for the two switches. (Ref:- Pin configurations of the two ICs), where  $\phi_1$  is the clock pulse of freq. =  $f_c$

**Observations**:-

$$V_i = ----- mV$$

, and  $f_c = ----- KHz$ ,

| S. No. | Signal freq.<br>f <sub>i</sub> (Hz) | V <sub>o</sub> = O/P Voltage<br>(mV) | $Gain = (V_0/V_i)$ |

|--------|-------------------------------------|--------------------------------------|--------------------|

| 1.     |                                     |                                      |                    |

| 2.     |                                     |                                      |                    |

| 3.     |                                     |                                      |                    |

| 4.     |                                     |                                      |                    |

| 5.     |                                     |                                      |                    |

| 6.     |                                     |                                      |                    |

| 7.     |                                     |                                      |                    |

| 8.     |                                     |                                      |                    |

| 9.     |                                     |                                      |                    |

| 10.    |                                     |                                      |                    |

| 11.    |                                     |                                      |                    |

| 12.    |                                     |                                      |                    |

Plot the frequency response curve (gain versus frequency),

#### Result:-

Practical value of the cut-off frequency obtained from the graph plotted is 490 Hz.

Designed value (given) = ----- Hz.

Hence, the percentage error = -----%.

#### **Experiment No. 03 (OTA Multi-function Filters)**

Object Analyze, design and experimentally verify the OTA – c multi-function filters for the LP, HP, BP and BE responses for a cut-off (pole) frequency of ..... KHz & Q = 1.

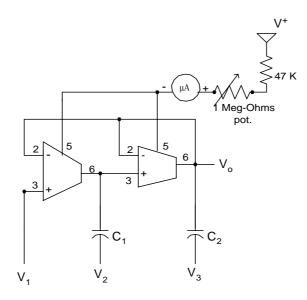

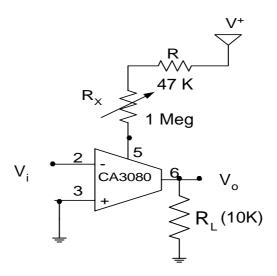

Circuit Diagram:-

Theory and Assumptions:-

$$V_{0} = \frac{s^{2}V_{3} + s\frac{g_{m2}}{C_{2}}V_{2} + \frac{g_{m1}}{C_{1}}\frac{g_{m2}}{C_{2}}V_{1}}{s^{2} + s\frac{g_{m2}}{C_{2}} + \frac{g_{m1}}{C_{1}}\frac{g_{m2}}{C_{2}}}$$

(3.1)

$$BW = \frac{\omega_0}{Q} = \frac{g_{m2}}{C_2} \quad ; \quad \omega_0 = \sqrt{\frac{g_{m1}g_{m2}}{C_1C_2}}$$

(3.2)

$$Q = \sqrt{\frac{g_{m1}C_2}{g_{m2}C_1}} \quad ; \quad g_{m1} = g_{m2} = \frac{I_B}{2V_T} = 19.23I_B$$

(3.3)

**Assumptions**:-

$$g_{m1} = g_{m2} = g_m = \frac{I_B}{2V_T} = 19.23I_B$$

,  $C_1 = C_2 = C$ ,  $Q = 1$

The cut-off (pole) frequency is given by:-

$$f_0 = \frac{19.23I_B}{2\pi C} = 3.062 \frac{I_B}{C}$$

----- (1)

The Band-width (BW) =  $\frac{\omega_o}{Q}$  =  $2\pi f_o$ ,

$$H_{HP} = H_{LP} = H_{BP} = H_{BE} = 1$$

,

#### **Operating Conditions**:-

For LPF:-

$$V_1 = V_1$$

, &  $V_2 = V_3 = 0$

For HPF:-

$$V_1 = V_3$$

, &  $V_2 = V_1 = 0$

For BPF:-

$$V_1 = V_2$$

, &  $V_1 = V_3 = 0$

For BEF:-

$$V_1 = V_1 = V_3$$

, &  $V_2 = 0$

Adjustment of I<sub>B</sub> by R<sub>x</sub>

$R_T = (R_x + R)$ , where  $R_x =$  variable resistor and R = fixed resistor

| $R_T$ ( $K\Omega$ )       | 100 | 150 | 200 | 300 | 600 |

|---------------------------|-----|-----|-----|-----|-----|

| Total I <sub>B</sub> (μA) | 150 | 100 | 75  | 50  | 25  |

DC Biasing Supply range = Symmetrical dual (+/- 6 to 18) volts

DC Biasing Supply used = Symmetrical dual (+/- 15) volts

#### Design:-

Given

$$f_0 = ---- KHz$$

, Assume  $I_B = ---- \mu A$

Calculate

$$C = ---- \mu F$$

,  $BW = (874.1 \times 10^6 I_B) Hz$ ,

Test the circuit band-width for  $I_B = 25 \mu A$ ,  $50 \mu A$  and  $100 \mu A$ .

#### **Observations**:-

$$V_0 = ---- mV$$

and  $I_B = ---- \mu A$ ,

#### 1. Readings for LPF:- $V_i = 20 \text{ mV}$

| S. No. | f <sub>i</sub> | Vo   | Gain (A) = |

|--------|----------------|------|------------|

|        | (KHz)          | (mV) | $V_o/V_i$  |

| 1.     | 0.1            |      |            |

| 2.     | 0.2            |      |            |

| 3.     | 0.5            |      |            |

| 4.     | 1.0            |      |            |

| 5.     | 1.5            |      |            |

| 6.     | 1.9            |      |            |

| 7.     | 2.5            |      |            |

| 8.     | 3.2            |      |            |

| 9.     | 4.2            |      |            |

| 10.    | 5.0            |      |            |

| 11.    | 5.5            |      |            |

| 12.    | 7.0            |      |            |

#### 2. Readings for HPF:- $V_i = 20 \text{ mV}$

| S. No. | fi    | $V_{o}$ | Gain (A)                        |

|--------|-------|---------|---------------------------------|

|        | (KHz) | (mV)    | $= \mathbf{V_o} / \mathbf{V_i}$ |

| 1.     | 0.1   |         |                                 |

| 2.     | 0.2   |         |                                 |

| 3.     | 0.5   |         |                                 |

| 4.     | 1.0   |         |                                 |

| 5.     | 1.5   |         |                                 |

| 6.     | 1.9   |         |                                 |

| 7.     | 2.5   |         |                                 |

| 8.     | 3.2   |         |                                 |

| 9.     | 4.2   |         |                                 |

| 10.    | 5.0   |         |                                 |

| 11.    |       |         |                                 |

Similarly take observations for BPF and Band Elimination (Notch) filters.

Plot the frequency response curves for LPF, HPF, BPF & BEF.

**Report:- 1.** Derive the expressions for the operating conditions.

2. Comment on the frequency responses obtained.

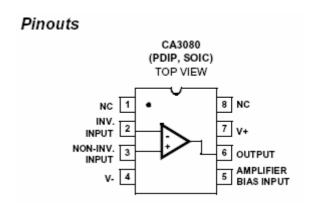

# Testing an OTA (CA3080)

Connect the OTA under test as shown in the following circuit diagram:-

- 1. Apply a sinusoidal signal of amplitude 50 mV $_{p-p}$  and frequency 2.0 KHz at Vi.

- 2. Observe the output signal.

- 3. If it is of opposite phase of the input and its amplitude is increasing by adjusting the variable resistance, then the OTA under test is all right.

- 4. If no signal is observed at the output, or the amplitude does not change by variable resistance, then the OTA is defective.

\*\*\*\*\*

### El 491 (Electronics Circuit Design Laboratory)

#### **Experiment No. 04 (Precision Rectifier)**

Object:- Design and experimentally verify the Full-wave and the Half-wave precision rectifier using bi-phase amplifier. Plot the output DC voltage versus input RMS voltage for the input signal between 0 volt and 1 volt.

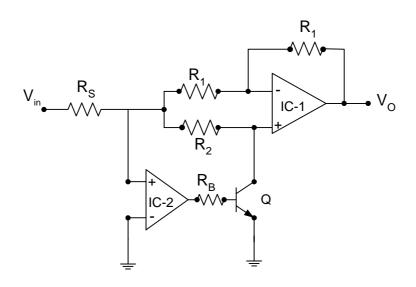

#### Circuit Diagram:-

$V_o = -V_{in}$ , when Q is ON,

$V_o = + V_{in}$ , when Q is OFF

Typically,  $V_{in} = 0.2 \text{ Volt}_{p-p} / 1.0 \text{ KHz Sine wave.}$

For Half-wave rectification, replace R1 by a short-circuit between pins # 2 and 6 of the IC-1.

- 1. Find the minimum input signal level for proper rectification at f = 200 Hz.

- <sub>2.</sub> Find the maximum signal frequency for proper rectification at  $V_{in} = 1.0 \text{ Volt}_{p-p}$

- 3. Trace the output waveforms for half-wave and full wave rectifiers.

#### **Components Used**:-

- 1) Opamp 741 (IC-1 & (IC-2)

- 2) NPN Transistor (Q) BC 147

- 3) Resistors:

#### El 491 (Electronics Circuit Design Laboratory)

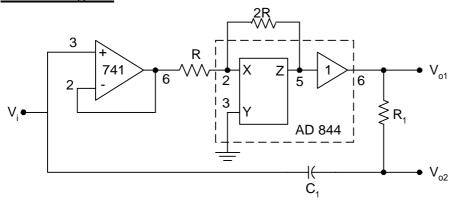

#### **Experiment No. 5 (CFA)**

Object:- Design an all pass section using CFA (AD844) for a pole frequency  $ω_p$  (=  $ω_z$ ) = 2  $πf_o$  ( $f_o$  = gp-no KHz). Plot the frequency response of the designed AP section (magnitude and phase of  $V_{o2}$  with respect to  $V_{i1}$  versus frequency).

#### Circuit Diagram:-

#### Design Equations: -

$$\frac{V_{o1}}{V_{i}} = -1$$

, ---- (1)

$$\frac{V_{o2}}{V_{i}} = \frac{s - \frac{1}{R_{1}C_{1}}}{s + \frac{1}{R_{1}C_{1}}} - \dots (2)$$

The pole frequency

$$\omega_{\mathbf{p}} = \omega_{\mathbf{z}} = \frac{1}{R_1 C_1}$$

---- (3)

$$(R = 10 \text{ K}\Omega, R_1 = 22 \text{ K}\Omega)$$

$(V_i = 0.4 V_{p-p} / 1.5 \text{ KHz})$  Sine wave may be used for initial testing of the designed circuit).

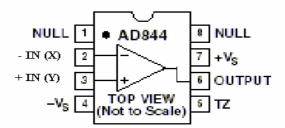

# Ratings of AD844 (60 MHz, 2000 V/µs Monolithic Op Amp):-

Wide-range of Biasing Power Supplies:  $\pm$  4.5 V to  $\pm$  18 V; Capable of high o/p drive of  $\pm$  50 mA to 50  $\Omega$ ; Low offset voltage: 150  $\mu$ V; Low Quiescent current: 6.5 mA; Large BW: 60 MHz at Gain of -1;

#### **Pin Connections:-**

# 8-Lead PDIP (N) and CERDIP (Q) Packages

#### Experiment No 06 (Opamp based Multi-function filter)

Object:- Analyze, design and experimentally verify the OPAMP based multifunction filter to realize low pass, high pass, band pass and band elimination responses for given cutoff (pole) frequency  $f_0 = \dots$  KHz.

#### Circuit Diagram:-

#### Theory and Analysis:-

On analyzing the circuit, the expression for  $V_0$  can be written as:

$$V_{o} = \frac{s^{2}V + s\frac{V_{2}}{R_{1}C} + V_{3}\frac{B}{R_{2}C}}{s^{2} + \frac{s}{C}\left[\frac{1}{R_{1}} + \frac{1}{R_{2}}\right] + \frac{B}{R_{2}C}}, \quad \dots$$

(1)

where B = unity-gain band width of the opamp.

$$\omega_0 = \sqrt{\frac{B}{R_2 C}} , \qquad Q = \frac{R_1}{R_1 + R_2} \sqrt{BCR_2}$$

**Design**:- Expression for

$$\mathbf{f_0} = \frac{1}{2\pi} \sqrt{\frac{B}{R_2 C}}$$

, ---- (2)

**Note:** For Opamp 741, select B in the range (0.4 - 1.5) MHz.

#### **Operating Conditions:**

With reference to the eqn (1) above, the circuit will be working as a multi function filter under the following conditions:

For Low pass filter:-  $V_1=V_2=0$ , and  $V_3=V_{in}$ , For High pass filter:-  $V_3=V_2=0$ , and  $V_1=V_{in}$ , For Band pass filter:-  $V_1=V_3=0$ , and  $V_2=V_{in}$ ,

For Band Elimination filter:-  $V_2 = 0$ , and  $V_1 = V_3 = V_{in}$ .

where 0 stands for grounded and  $V_{in}$  for the input signal.

#### **Observations:**

Given  $f_0 = \ldots KHz$ Take  $R_1 = R_2 = \ldots K\Omega$ Calculate  $C = \ldots nF$ , Use the nearest available value of  $C = \ldots \mu F$ , By back calculation,  $f_0 = V_{in} = \ldots volts_{p-p}$

#### (i) Readings for low pass filter:-

| S. No. | Freq. of V <sub>in</sub> (Hz) | Amplitude of V <sub>o p-p</sub> (mV) | Gain, $A = \frac{V_o}{V_{in}}$ |

|--------|-------------------------------|--------------------------------------|--------------------------------|

|        |                               |                                      |                                |

|        |                               |                                      |                                |

|        |                               |                                      |                                |

|        |                               |                                      |                                |

|        |                               |                                      |                                |

|        |                               |                                      |                                |

|        |                               |                                      |                                |

Similarly tabulate:-

- (ii) Readings for high pass filter:-

- (iii) Readings for band pass filter:-

- (iv) Readings for band elimination filter:-

Measure  $f_0$  from the frequency-response curve.

**Report**:- Plot frequency response of each filter on the same semi-log graph paper and verify the designed cutoff frequency  $f_o$ . Also give your comments on the results and carry out circuit analysis.

\*\*\*\*\*\*

#### **APPENDIX - I**

#### **Some Common Precautions**

Care should be taken to observe the following Precautions while performing experiments ON the circuits employing Electronic Devices:-

- 1. Before connecting the device into the circuit, always ensure that the device is perfectly working; that is, it should have already been tested separately in its test-circuit.

- 2. Always connect the device/IC carefully and correctly into the circuit being assembled on the Breadboard to avoid any loose or incorrect connection leading to the damage of the device.

- 3. While connecting the device into the circuit on the breadboard, ensure that no DC supply or signal is connected to that circuit. (Keep power supplies and signal generators OFF).

- 4. When the device has been correctly connected into the circuit, only then turn ON the DC supply and the signal generators in this order:- "Firstly turn ON the Power Supply; then turn ON the signal generator".

- 5. Don't forget to check the output voltage of the DC power supply before connecting it to the circuit, and adjust it to proper value conforming to the device specifications.

- 6. Don't forget to adjust the amplitude of the signal to be connected to the device, to its proper value, always below the maximum signal level specified in the device data sheet, to avoid the consequent damage to the device already checked and found OK.

- 7. Take extra care while using the costly and sensitive devices like OTAs and Current conveyers, that is, read thoroughly their specifications given in their datasheets, and never violate any rating of the device.

- 8. Before replacing any device or component on the bread-board, turn-OFF the signal generator first and then turn-OFF the power supplies connected to the circuit, and then replace the device or component; and after replacement, switch ON the power supply first & then switch ON the signal generator.

\*\*\*\*\*\*

#### APPENDIX - II

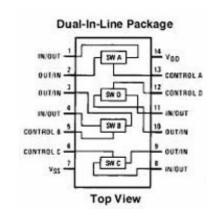

Pin Connections and the Specifications of the ICs: CD 4066 and OTA CA 3080

#### CD4066BM/CD4066BC Quad Bilateral Switch

#### **Features**

| ■ Wide supply voltage range                  | 3V to 15V                                                    |

|----------------------------------------------|--------------------------------------------------------------|

| <ul> <li>High noise immunity</li> </ul>      | 0.45 V <sub>DD</sub> (typ.)                                  |

| ■ Wide range of digital and                  | ±7.5 VPEAK                                                   |

| analog switching                             |                                                              |

| <ul><li>"ON" resistance for 15V or</li></ul> | peration 80Ω                                                 |

| ■ Matched "ON" resistance                    | $\Delta R_{ON} = 5\Omega$ (typ.)                             |

| over 15V signal input                        |                                                              |

| <ul><li>"ON" resistance flat over</li></ul>  | peak-to-peak signal range                                    |

| ■ High "ON"/"OFF"                            | 65 dB (typ.)                                                 |

| output voltage ratio                         | $@$ f <sub>is</sub> = 10 kHz, R <sub>L</sub> = 10 k $\Omega$ |

| ■ High degree linearity                      | 0.1% distortion (typ.)                                       |

| High degree linearity                        | @ $f_{is} = 1 \text{ kHz}, V_{is} = 5V_{p-p}$                |

| High degree linearity                        | $V_{DD}-V_{SS}=10V$ , $R_L=10~k\Omega$                       |

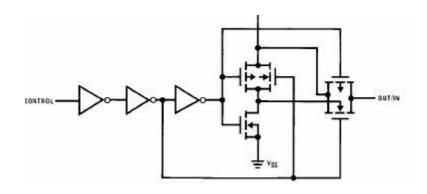

#### Schematic Diagram:-

#### Absolute Maximum Ratings (Notes 1 & 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

$\begin{array}{lll} \text{Supply Voltage (V_{DD})} & -0.5 \text{V to } + 18 \text{V} \\ \text{Input Voltage (V_{IN})} & -0.5 \text{V to V}_{DD} + 0.5 \text{V} \\ \text{Storage Temperature Range (Ts)} & -65 ^{\circ} \text{C to } + 150 ^{\circ} \text{C} \end{array}$

Power Dissipation (PD)

Dual-In-Line 700 mW Small Outline 500 mW

Lead Temperature (T<sub>L</sub>)

(Soldering, 10 seconds) 300°C

# Recommended Operating

Conditions (Note 2)

CD4066BM -55°C to +125°C CD4066BC -40°C to +85°C

For further details, refer to the manufacturer's Datasheet

M. Hadi Ali Khan Electronics Engineer

# CA 3080 2MHz, Operational Transconductance Amplifier (OTA)

# Features • Slew Rate (Unity Gain, Compensated) 50V/μs • Adjustable Power Consumption 10μW to 30μW • Flexible Supply Voltage Range ±2V to ±15V • Fully Adjustable Gain 0 to g<sub>M</sub>R<sub>L</sub> Limit • Tight g<sub>M</sub> Spread: 2:1 • CA3080 2:1 • CA3080A 1.6:1 • Extended g<sub>M</sub> Linearity 3 Decades

#### Absolute Maximum Ratings

| Supply Voltage (Between V+ and V- Terminal) 36     | δV |

|----------------------------------------------------|----|

| Differential Input Voltage                         | 5V |

| Input Voltage                                      | V- |

| Input Signal Current                               | nΑ |

| Amplifier Bias Current (I <sub>ABC</sub> )         | nΑ |

| Output Short Circuit Duration (Note 1) No Limitati | on |

Take  $I_B < \, 500 \mu A \,$  &  $\, V_i < 100 \; mV$

The CA3080 and CA3080A types have differential input and a single-ended, push-pull, class-A output. In addition, these types have an amplifier bias input which may be used either for gating or for linear gain control. These types also have a high output impedance and their transconductance (gM) is directly proportional to the amplifier bias current (I<sub>ABC</sub>).

The CA3080 and CA3080A types are notable for their excellent slew rate  $(50V/\mu s)$ , which makes them especially useful for multiplexer and fast unity-gain voltage followers. These types are especially applicable for multiplexer applications because power is consumed only when the devices are in the "ON" channel state.

For further details, refer to the manufacturer's Datasheet

# Compiled by:-

## M. Hadi Ali Khan

B. Sc. Engg. (Alig.); Ex-MIEEE (USA); Ex-AMIETE (India); Ex-MSSI (India)

#### **Electronics Engineer**;

Department of Electronics Engineering, AMU, Aligarh – 202 002

Res: - 5-B, Zakaullah Road, Tar Bangla, AMU, Aligarh-202 002

Email: hadialikhan@gmail.com

**Phone & Fax No**:- (0571) -2721148